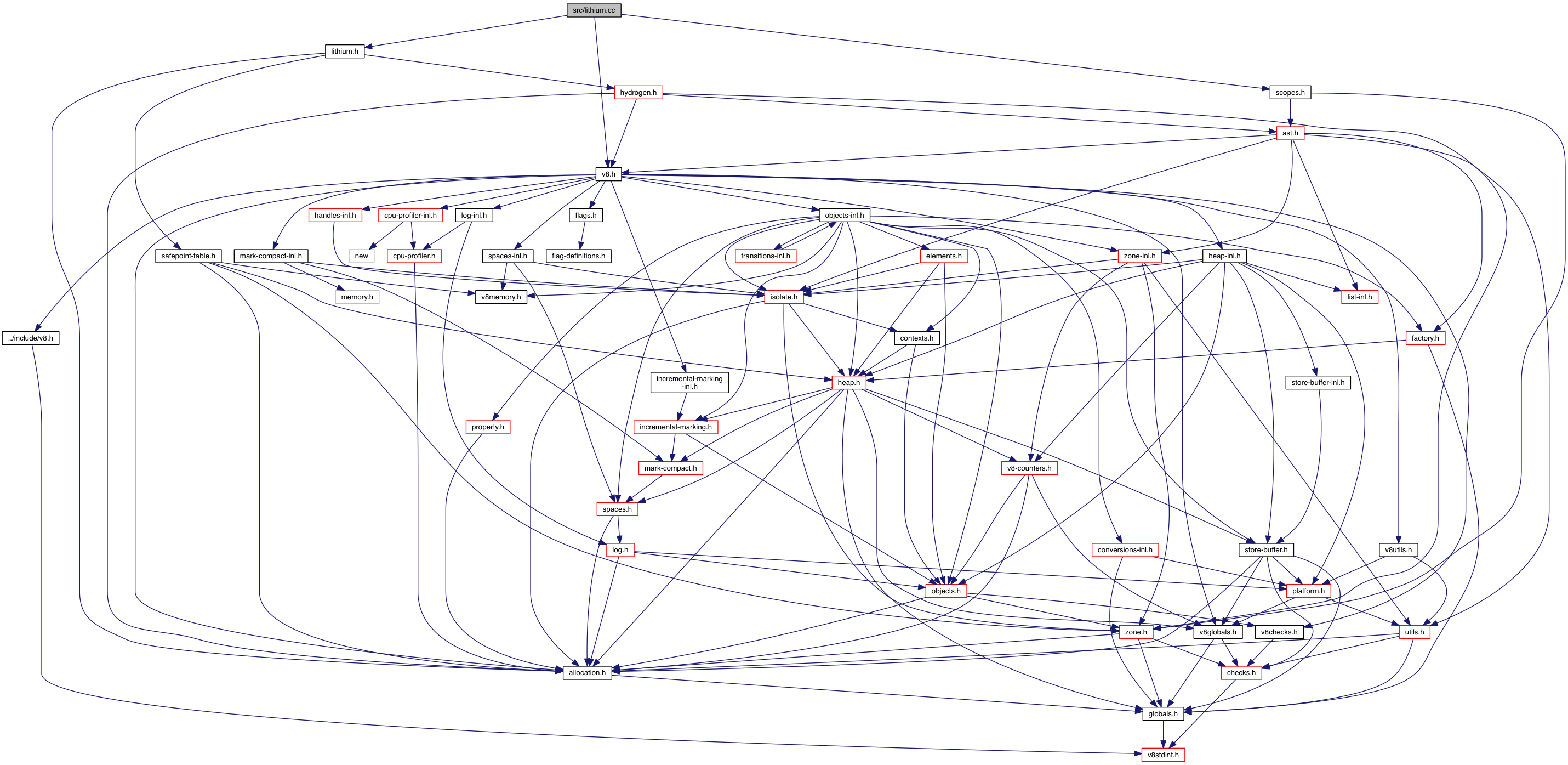

#include "v8.h"

#include "lithium.h"

#include "scopes.h"

Go to the source code of this file.

| #define DEFINE_OPERAND_CACHE |

( |

|

name, |

|

|

|

type |

|

) |

| |

Value:L##name*

L##name::cache =

NULL; \

\

void

L##name::SetUpCache() { \

if (cache) return; \

cache = new

L##name[kNumCachedOperands]; \ for (int i = 0; i < kNumCachedOperands; i++) { \

cache[i].ConvertTo(type, i); \

} \

} \

\

void L##name::TearDownCache() { \

delete[] cache; \

}

activate correct semantics for inheriting readonliness enable harmony semantics for typeof enable harmony enable harmony proxies enable all harmony harmony_scoping harmony_proxies harmony_scoping tracks arrays with only smi values automatically unbox arrays of doubles use crankshaft use hydrogen range analysis use hydrogen global value numbering use function inlining maximum number of AST nodes considered for a single inlining loop invariant code motion print statistics for hydrogen trace generated IR for specified phases trace register allocator trace range analysis trace representation types environment for every instruction put a break point before deoptimizing polymorphic inlining perform array bounds checks elimination use dead code elimination trace on stack replacement optimize closures cache optimized code for closures functions with arguments object loop weight for representation inference allow uint32 values on optimize frames if they are used only in safe operations track parallel recompilation enable all profiler experiments number of stack frames inspected by the profiler call recompile stub directly when self optimizing trigger profiler ticks based on counting instead of timing weight back edges by jump distance for interrupt triggering percentage of ICs that must have type info to allow optimization watch_ic_patching retry_self_opt interrupt_at_exit extra verbose compilation tracing generate extra emit comments in code disassembly enable use of SSE3 instructions if available enable use of CMOV instruction if available enable use of SAHF instruction if enable use of VFP3 instructions if available this implies enabling ARMv7 and VFP2 enable use of VFP2 instructions if available enable use of SDIV and UDIV instructions if enable loading bit constant by means of movw movt instruction enable unaligned accesses for enable use of MIPS FPU instructions if NULL

Definition at line 114 of file lithium.cc.

| #define LITHIUM_OPERAND_SETUP |

( |

|

name, |

|

|

|

type |

|

) |

| L##name::SetUpCache(); |

| #define LITHIUM_OPERAND_TEARDOWN |

( |

|

name, |

|

|

|

type |

|

) |

| L##name::TearDownCache(); |