|

v8

3.11.10(node0.8.26)

V8 is Google's open source JavaScript engine

|

|

v8

3.11.10(node0.8.26)

V8 is Google's open source JavaScript engine

|

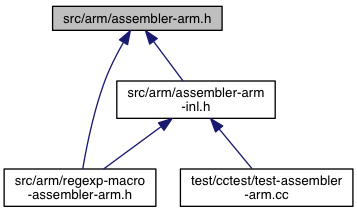

Go to the source code of this file.

Data Structures | |

| struct | Register |

| struct | SwVfpRegister |

| struct | DwVfpRegister |

| struct | CRegister |

| class | BASE_EMBEDDED< Visitor > |

| class | BASE_EMBEDDED< Visitor > |

| class | CpuFeatures |

| class | CpuFeatures::BASE_EMBEDDED |

| class | CpuFeatures::BASE_EMBEDDED |

| class | Assembler |

| class | Assembler::BlockConstPoolScope |

| class | BASE_EMBEDDED< Visitor > |

Namespaces | |

| v8 | |

| v8::internal | |

Macros | |

| #define | kFirstCalleeSavedDoubleReg d8 |

| #define | kLastCalleeSavedDoubleReg d15 |

| #define | kDoubleRegZero d14 |

| #define | kScratchDoubleReg d15 |

Typedefs | |

| typedef DwVfpRegister | DoubleRegister |

Enumerations | |

| enum | Coprocessor { p0 = 0, p1 = 1, p2 = 2, p3 = 3, p4 = 4, p5 = 5, p6 = 6, p7 = 7, p8 = 8, p9 = 9, p10 = 10, p11 = 11, p12 = 12, p13 = 13, p14 = 14, p15 = 15 } |

Variables | |

| const int | kRegister_no_reg_Code = -1 |

| const int | kRegister_r0_Code = 0 |

| const int | kRegister_r1_Code = 1 |

| const int | kRegister_r2_Code = 2 |

| const int | kRegister_r3_Code = 3 |

| const int | kRegister_r4_Code = 4 |

| const int | kRegister_r5_Code = 5 |

| const int | kRegister_r6_Code = 6 |

| const int | kRegister_r7_Code = 7 |

| const int | kRegister_r8_Code = 8 |

| const int | kRegister_r9_Code = 9 |

| const int | kRegister_r10_Code = 10 |

| const int | kRegister_fp_Code = 11 |

| const int | kRegister_ip_Code = 12 |

| const int | kRegister_sp_Code = 13 |

| const int | kRegister_lr_Code = 14 |

| const int | kRegister_pc_Code = 15 |

| const Register | no_reg = { kRegister_no_reg_Code } |

| const Register | r0 = { kRegister_r0_Code } |

| const Register | r1 = { kRegister_r1_Code } |

| const Register | r2 = { kRegister_r2_Code } |

| const Register | r3 = { kRegister_r3_Code } |

| const Register | r4 = { kRegister_r4_Code } |

| const Register | r5 = { kRegister_r5_Code } |

| const Register | r6 = { kRegister_r6_Code } |

| const Register | r7 = { kRegister_r7_Code } |

| const Register | r8 = { kRegister_r8_Code } |

| const Register | r9 = { kRegister_r9_Code } |

| const Register | r10 = { kRegister_r10_Code } |

| const Register | fp = { kRegister_fp_Code } |

| const Register | ip = { kRegister_ip_Code } |

| const Register | sp = { kRegister_sp_Code } |

| const Register | lr = { kRegister_lr_Code } |

| const Register | pc = { kRegister_pc_Code } |

| const SwVfpRegister | s0 = { 0 } |

| const SwVfpRegister | s1 = { 1 } |

| const SwVfpRegister | s2 = { 2 } |

| const SwVfpRegister | s3 = { 3 } |

| const SwVfpRegister | s4 = { 4 } |

| const SwVfpRegister | s5 = { 5 } |

| const SwVfpRegister | s6 = { 6 } |

| const SwVfpRegister | s7 = { 7 } |

| const SwVfpRegister | s8 = { 8 } |

| const SwVfpRegister | s9 = { 9 } |

| const SwVfpRegister | s10 = { 10 } |

| const SwVfpRegister | s11 = { 11 } |

| const SwVfpRegister | s12 = { 12 } |

| const SwVfpRegister | s13 = { 13 } |

| const SwVfpRegister | s14 = { 14 } |

| const SwVfpRegister | s15 = { 15 } |

| const SwVfpRegister | s16 = { 16 } |

| const SwVfpRegister | s17 = { 17 } |

| const SwVfpRegister | s18 = { 18 } |

| const SwVfpRegister | s19 = { 19 } |

| const SwVfpRegister | s20 = { 20 } |

| const SwVfpRegister | s21 = { 21 } |

| const SwVfpRegister | s22 = { 22 } |

| const SwVfpRegister | s23 = { 23 } |

| const SwVfpRegister | s24 = { 24 } |

| const SwVfpRegister | s25 = { 25 } |

| const SwVfpRegister | s26 = { 26 } |

| const SwVfpRegister | s27 = { 27 } |

| const SwVfpRegister | s28 = { 28 } |

| const SwVfpRegister | s29 = { 29 } |

| const SwVfpRegister | s30 = { 30 } |

| const SwVfpRegister | s31 = { 31 } |

| const DwVfpRegister | no_dreg = { -1 } |

| const DwVfpRegister | d0 = { 0 } |

| const DwVfpRegister | d1 = { 1 } |

| const DwVfpRegister | d2 = { 2 } |

| const DwVfpRegister | d3 = { 3 } |

| const DwVfpRegister | d4 = { 4 } |

| const DwVfpRegister | d5 = { 5 } |

| const DwVfpRegister | d6 = { 6 } |

| const DwVfpRegister | d7 = { 7 } |

| const DwVfpRegister | d8 = { 8 } |

| const DwVfpRegister | d9 = { 9 } |

| const DwVfpRegister | d10 = { 10 } |

| const DwVfpRegister | d11 = { 11 } |

| const DwVfpRegister | d12 = { 12 } |

| const DwVfpRegister | d13 = { 13 } |

| const DwVfpRegister | d14 = { 14 } |

| const DwVfpRegister | d15 = { 15 } |

| const CRegister | no_creg = { -1 } |

| const CRegister | cr0 = { 0 } |

| const CRegister | cr1 = { 1 } |

| const CRegister | cr2 = { 2 } |

| const CRegister | cr3 = { 3 } |

| const CRegister | cr4 = { 4 } |

| const CRegister | cr5 = { 5 } |

| const CRegister | cr6 = { 6 } |

| const CRegister | cr7 = { 7 } |

| const CRegister | cr8 = { 8 } |

| const CRegister | cr9 = { 9 } |

| const CRegister | cr10 = { 10 } |

| const CRegister | cr11 = { 11 } |

| const CRegister | cr12 = { 12 } |

| const CRegister | cr13 = { 13 } |

| const CRegister | cr14 = { 14 } |

| const CRegister | cr15 = { 15 } |

| const Instr | kMovLrPc |

| const Instr | kLdrPCMask |

| const Instr | kLdrPCPattern |

| const Instr | kBlxRegMask |

| const Instr | kBlxRegPattern |

| const Instr | kBlxIp |

| const Instr | kMovMvnMask |

| const Instr | kMovMvnPattern |

| const Instr | kMovMvnFlip |

| const Instr | kMovLeaveCCMask |

| const Instr | kMovLeaveCCPattern |

| const Instr | kMovwMask |

| const Instr | kMovwPattern |

| const Instr | kMovwLeaveCCFlip |

| const Instr | kCmpCmnMask |

| const Instr | kCmpCmnPattern |

| const Instr | kCmpCmnFlip |

| const Instr | kAddSubFlip |

| const Instr | kAndBicFlip |

| #define kDoubleRegZero d14 |

Definition at line 331 of file assembler-arm.h.

Referenced by DwVfpRegister::ToAllocationIndex(), and FPURegister::ToAllocationIndex().

| #define kFirstCalleeSavedDoubleReg d8 |

Definition at line 329 of file assembler-arm.h.

| #define kLastCalleeSavedDoubleReg d15 |

Definition at line 330 of file assembler-arm.h.

| #define kScratchDoubleReg d15 |

Definition at line 332 of file assembler-arm.h.

Referenced by DwVfpRegister::ToAllocationIndex().